The semiconductor industry followed Moore’s Law over the last fifty years. Limitations on the continued CMOS technology scaling and today’s emerging applications with strict requirements in terms of performance and power consumption pose significant challenges to device technology and computer architecture. Moore’s Law was extrapolated in three different domains denominated, More Moore, More Than Moore and Beyond Moore. Considering the domain Beyond Moore, the use of new device technology is being explored to complement and/or replace CMOS technology. Memristive devices represent one of the most promising candidates due to encouraging characteristics such as their CMOS manufacturing compatibility, zero standby power consumption, high scalability, and density as well as to the fact that these devices can not only implement memory, but also computing elements, addressing issues related to the von Neumann architectures.

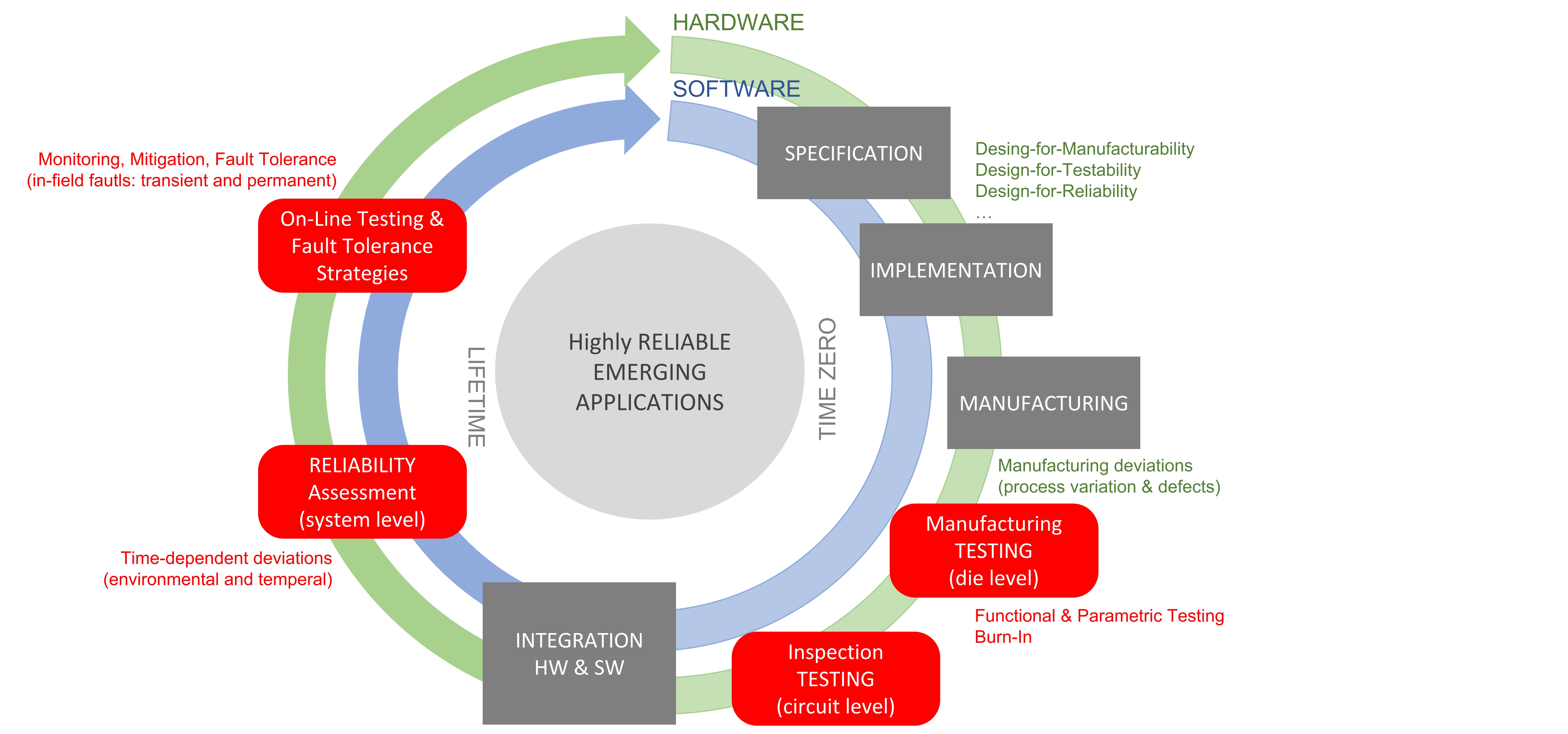

However, the use of novel devices, such as memristive devices, for implementing emerging applications depends on being able to guarantee their quality after manufacturing as well as their reliability during lifetime. This activity targets on the research of topics such as:

- Fault Model & Defect Injection Schemes for Novel Devices;

- Manufacturing Test of Emerging Technology-Based Systems;

- Reliability-Aware Design of Emerging Applications: On-Line Testing, Monitoring and Mitigating Solutions and Fault Tolerance Strategies;

- Reliability Assessment based on Fault Injection Platforms (Time-Dependent Deviations).

This research activity also addresses main challenges related to the integration of emerging technologies with CMOS at Device, Circuit, and System Level.

[E. Brum, T. S. Copetti, L. B. Bolzani Poehls et al., “Evaluating the impact of process variation on RRAMs,” LATS, 2021, doi: 10.1109/LATS53581.2021.9651789 , pdf]

[T. S. Copetti et al., “Validating a DFT Strategy’s Detection Capability regarding Emerging Faults in RRAMs,” VLSI-SoC, 2021, doi: 10.1109/VLSI-SoC53125.2021.9606993 , pdf]