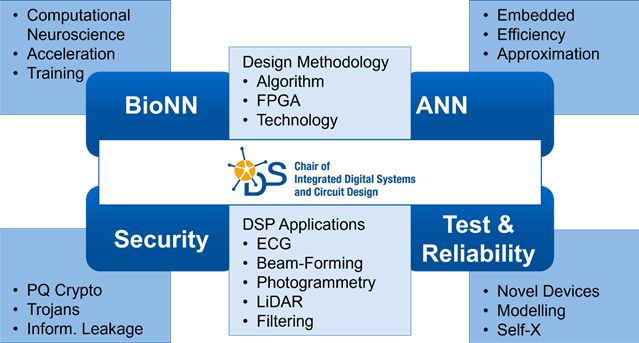

The research activities of the chair focus on novel architectures as well as circuit level concepts and design methodologies to implement energy and area efficient integrated circuits (‘chips’) in modern – so-called nanometer CMOS technologies. The novel strategies, concepts and methodologies are developed based on application examples in the general domain of high-throughput digital signal processing. Thereby, focal areas are biological as well as artificial neural networks, security and test & reliability. Fundamentally, they all evolve around a physically oriented design approach. The design complexity handled at the chair goes up to 200 Million transistors for a 28nm CMOS technology. An overview of the different research fields can be found on the left.

Research areas